UHI互连技术:重塑数据中心存储架构

问题意识

High Performance RAID With Universal High-Performance Interconnect (UHI)

Barry Pangrle Abacus Semiconductor Corp.

背景介绍

在数据爆炸式增长的时代,存储系统面临着严峻的性能与成本平衡挑战。您是否曾思考过:为什么HDD在成本上具有巨大优势,却难以满足高性能需求?为什么SSD成本下降速度放缓,无法完全取代HDD?Abacus半导体公司提出的UHI通用高性能互连技术,正是为了解决这一核心矛盾。基于最先进的112G SerDes物理层,UHI每个端口提供224GB/s的单向带宽,远超PCIe 5.0。这项技术如何通过Chiplet架构和硬件RAID加速核,构建出兼具HDD成本效益和SSD性能表现的创新解决方案?本文将带您深入探索UHI技术如何重新定义数据中心存储架构。

阅读收获

- 理解HDD在成本上的持久优势(约6倍于SSD)及其技术演进路径

- 掌握UHI互连技术的核心架构,包括其基于PCIe 6.0的物理层设计和896GB/s的聚合带宽能力

- 了解如何通过硬件RAID加速核和智能缓存技术优化HDD性能瓶颈

- 认识分解式架构和内存池化技术在下一代数据中心中的关键作用

开放性问题

- UHI技术宣称的统一互联如何平衡GPU等高带宽组件与CPU、I/O等低带宽需求的差异化?

- 在CXL技术快速发展的背景下,UHI在内存池化方面有哪些独特的技术优势?

- 您认为基于Chiplet的模块化服务器架构,在实际部署中会面临哪些主要的工程挑战?

👉 划线高亮 观点批注

Main

PPT清晰地阐述了本次演讲的“为什么做”、“做什么”和“怎么做”。

-

核心问题(Why): 如何在保留大容量HDD巨大成本优势的同时,克服其固有的性能瓶行,构建一个高性能的存储系统。

-

核心方案(What): 提出一个软硬件结合的高性能RAID解决方案。

-

实现路径(How):

-

软件/算法层:利用智能缓存和NCQ技术来优化对HDD的访问模式,提高I/O效率。

-

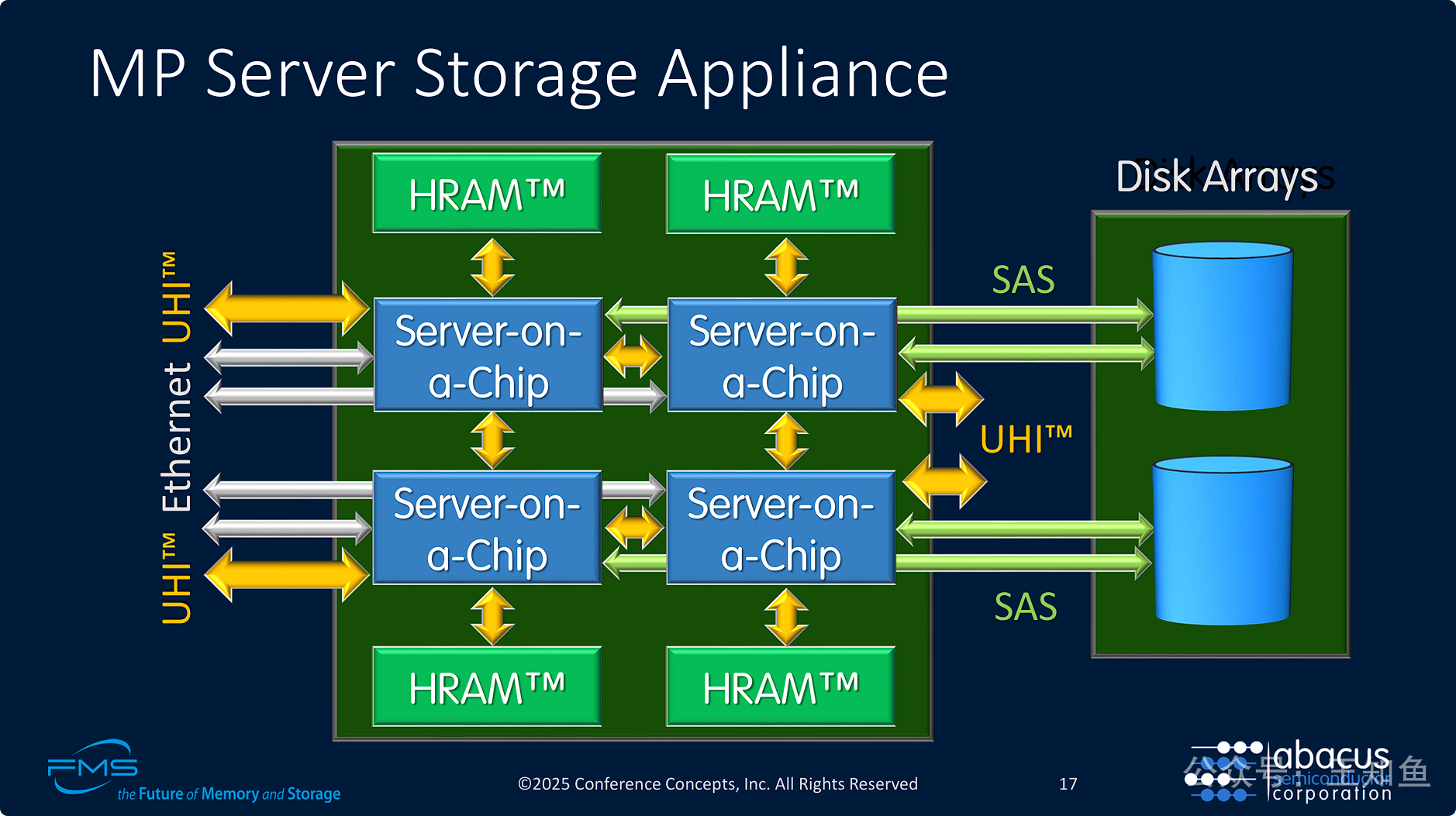

硬件/物理层:基于一个集成了RAID控制器的定制化SoC,并采用其专有的 UHI™ 互连技术作为系统的高速总线,为整个方案提供强大的性能基础。

-

Abacus公司的策略是通过一个集成的SoC平台,用软件智能(NCQ和缓存)来弥补HDD的性能短板,同时用其核心硬件技术(UHI™)来保证整个系统内部没有瓶颈,最终实现一个兼具HDD成本效益和高性能的存储解决方案。

-

主要观点: HDD在每TB成本上相对于SSD拥有巨大且持久的优势。这种优势在可预见的未来(至2028年)不仅不会消失,反而会稳定地保持在10倍以上。

-

关键技术支撑: 对于HDD而言,新的MAMR(微波辅助磁记录)技术是其继续降低成本、保持竞争优势的关键。对于SSD,尽管技术在进步(QLC),但其成本下降的速度正在放缓。

-

驳斥“交叉点”理论: 该图表有力地反驳了市场上流传的“SSD和HDD成本将在某一天持平(出现交叉点)”的观点。

-

演讲逻辑支撑: 这张图为上一页PPT中提出的问题——“为什么要费力优化HDD性能?”——提供了强有力的答案。正因为HDD在成本上具有如此巨大的吸引力,为它开发高性能的解决方案(如Abacus公司所做的)才具有重大的市场价值和现实意义。

从最新数据来看,有2点需要更新:

- 可预见的未来 HDD/SSD 的成本优势,没有10倍之高,缩小到6倍左右

- HDD容量密度攀升,大概率是借助HARM(热辅助磁记录)技术,而不是MARM

参考阅读:WD:数据中心HDD的成本与未来

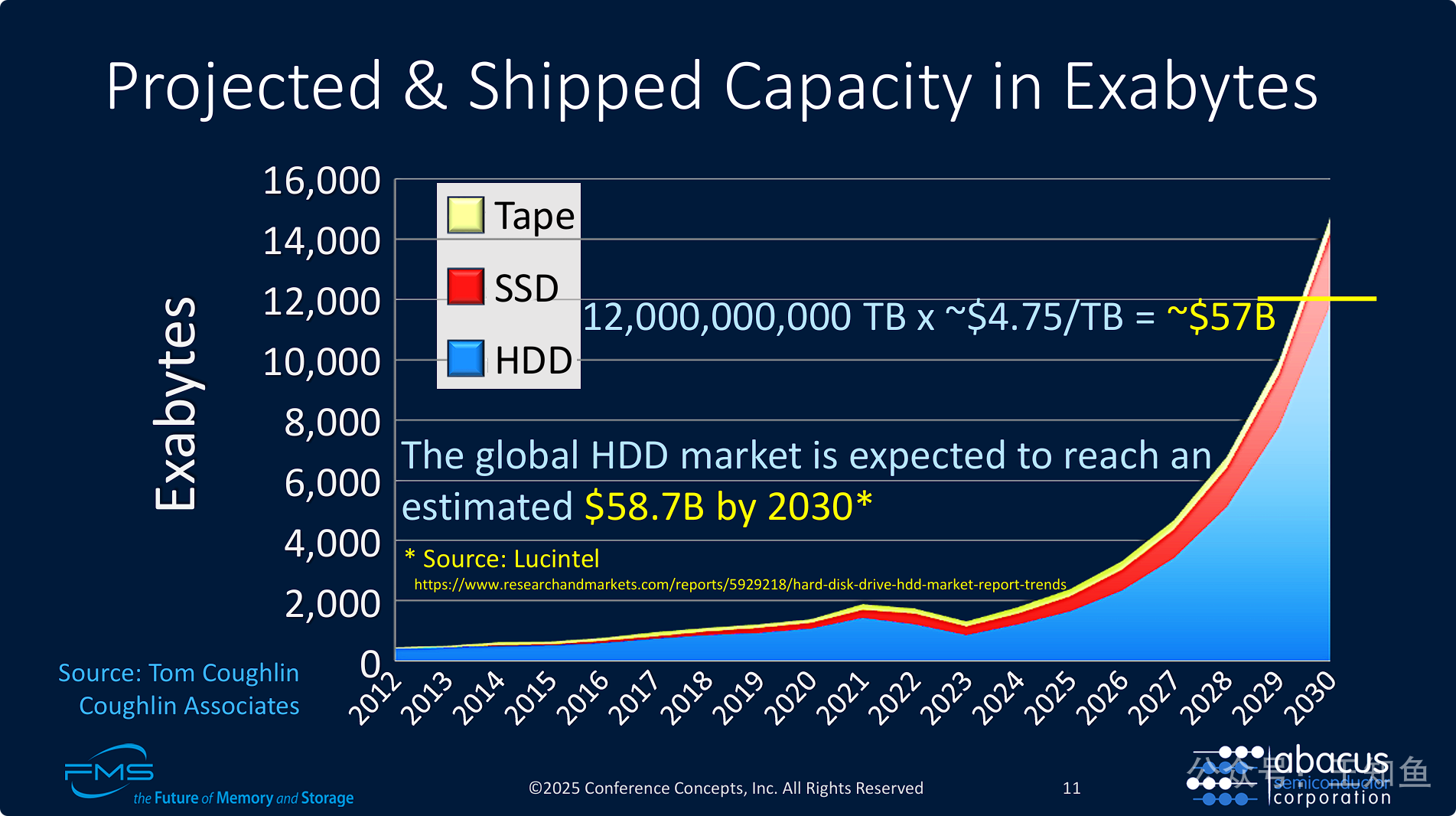

PPT的核心目的是从市场总容量和市场价值两个维度,进一步强化HDD在未来存储领域不可动摇的重要性。

-

容量为王: 核心观点是,就出货的总容量而言,HDD是并且在未来十年内仍将是绝对的市场统治者。全球数据量的爆炸性增长主要由成本更低的HDD来满足。

-

巨大的市场价值: 这种容量上的主导地位直接转化为巨大的商业价值。到2030年,HDD本身仍将是一个接近600亿美元的庞大市场。这证明了投资于HDD技术创新(如Abacus公司的方案)具有充分的商业回报前景。

PPT是对前面几页数据图表的提炼和总结,将HDD的优势从量化的数据(成本、容量)转化为定性的、易于理解的五大核心价值主张。

-

核心信息: HDD不会被SSD完全取代,因为它们在存储生态系统中扮演着独特且关键的角色。

-

价值总结: HDD的核心价值可以归纳为:可靠性 (适合长期存储)、经济性 (适合海量数据)、适用性 (适合冷数据)、协同性 (可与SSD构建混合系统) 和 系统性 (在存储分层中地位稳固)。

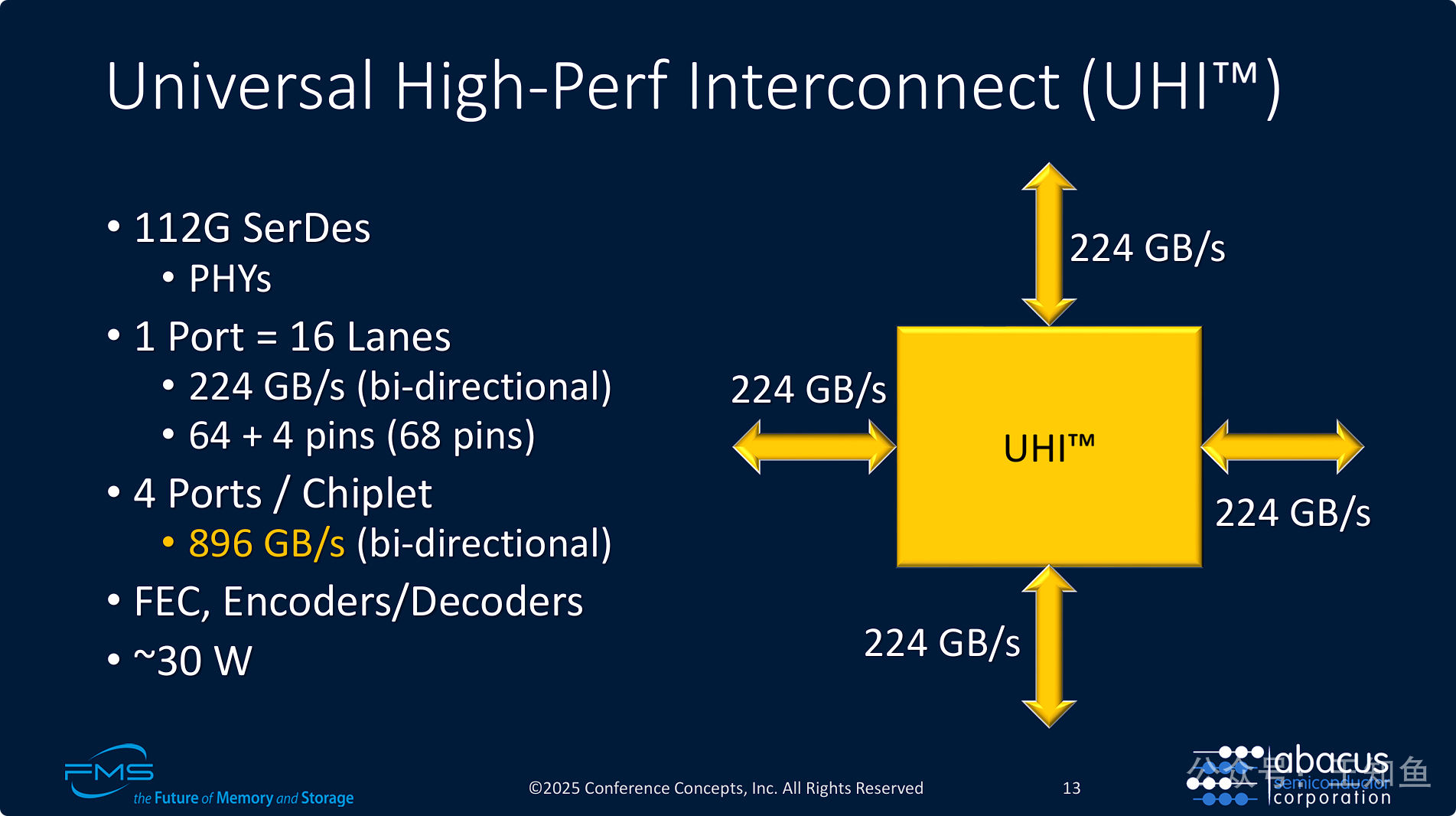

本次演讲的技术核心展示,它用具体的性能数据定义了UHI™是什么,以及它为什么是“高性能”的。

-

顶尖的物理层技术: UHI基于业界最前沿的 112G SerDes 技术构建,这是其实现超高带宽的基石。

-

极高的端口带宽: 每个UHI端口(x16)能提供 224 GB/s 的单向带宽,这个速度远超现有的通用总线(如PCIe 5.0 x16 为 64 GB/s)。

-

惊人的聚合吞吐能力: 通过Chiplet架构,单颗芯片即可提供四个这样的端口,实现高达 896 GB/s 的总聚合带宽,为大规模数据交换提供了强大的硬件基础。

-

完整与可靠: UHI不仅追求速度,还内置了FEC等关键功能来保证高速传输的可靠性,并给出了功耗参考值,表明了其设计的完整性。

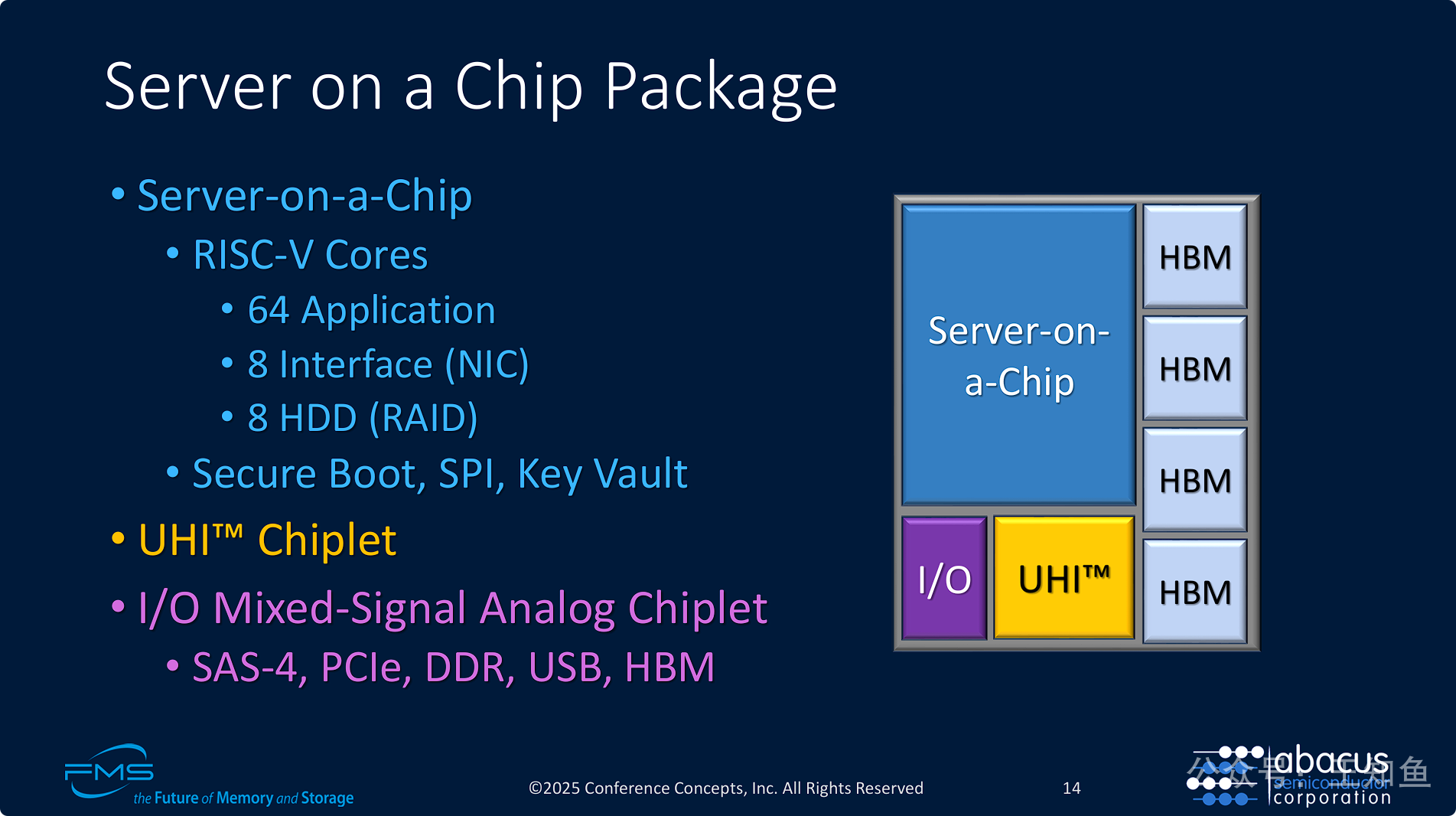

PPT是整个技术方案的“解剖图”,它清晰地展示了Abacus公司如何通过硬件设计来实现其宣称的高性能目标。

-

先进的Chiplet架构: 整个系统并非传统的单片SoC,而是采用了将不同功能的芯粒(计算、I/O、互连)封装在一起的先进Chiplet模式。这种模式可以更好地平衡成本、良率和性能。

-

专核专用的异构计算: SoC内部没有使用同构的核心,而是为应用、网络和存储(RAID) 配备了专门的RISC-V处理器核心。通过 硬件RAID加速核 ,可以极大地提升RAID运算效率,减轻主CPU的负担。

-

顶级的高性能组件集成: 该方案整合了三大高性能技术:

-

HBM: 提供超高的内存带宽。

-

UHI™: 提供超高的片间/系统间互连带宽。

-

专用RAID核: 提供高效的存储处理能力。

-

-

完整的“服务器”定义: 这个封装模块集成了计算、内存、存储接口(SAS)、网络接口(由专用核处理)和系统互连,名副其实地构成了一个“片上服务器”,特别是针对存储密集型应用。

===

“Server on a Chip” (SoC) 的理念是将传统服务器主板上的多个独立关键组件——例如中央处理器(CPU)、内存控制器、网络接口卡(NIC)、RAID卡/存储控制器等——全部集成到一个单一的、高度集成的芯片(或本例中的“芯片封装”)中

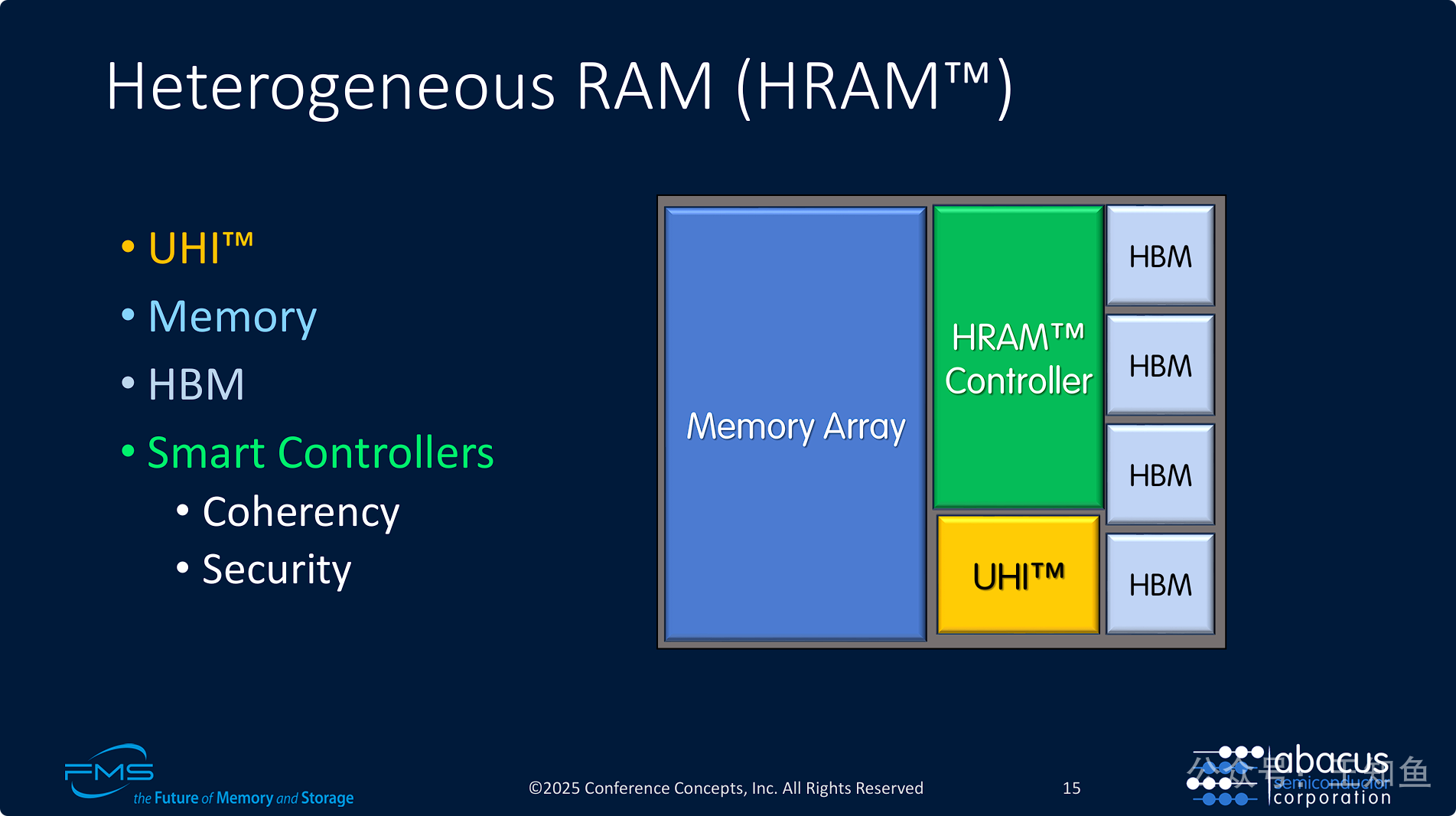

Abacus生态系统中的“内存”解决方案,它同样不是一个标准组件,而是一个高度创新的智能系统。

-

核心概念: HRAM™是一种智能化的、分层的、池化的内存系统。它将不同特性(如高带宽的HBM和高容量的DRAM)的内存介质“异构”地组合在一起,并通过一个智能控制器进行统一管理。

-

分层内存架构: HRAM内部构建了一个内存层级:HBM作为高速缓存层(L-something Cache),主内存阵列作为容量层。智能控制器会自动管理数据在这两层之间的流动,将热数据放在HBM中加速访问。

-

通过UHI™实现内存池化: HRAM模块通过UHI总线接入系统,这意味着内存可以脱离CPU主板,成为一个独立的、可通过网络访问的“内存池”。多个“片上服务器”(SoC)可以连接到同一个或多个HRAM模块,实现内存资源的共享和灵活扩展,这是数据中心下一代架构(如CXL技术所倡导的)的重要方向。

-

超越内存,提供高级服务: HRAM控制器提供的一致性和安全性功能,表明它不仅仅是一个内存设备,更是一个主动管理数据的智能节点。

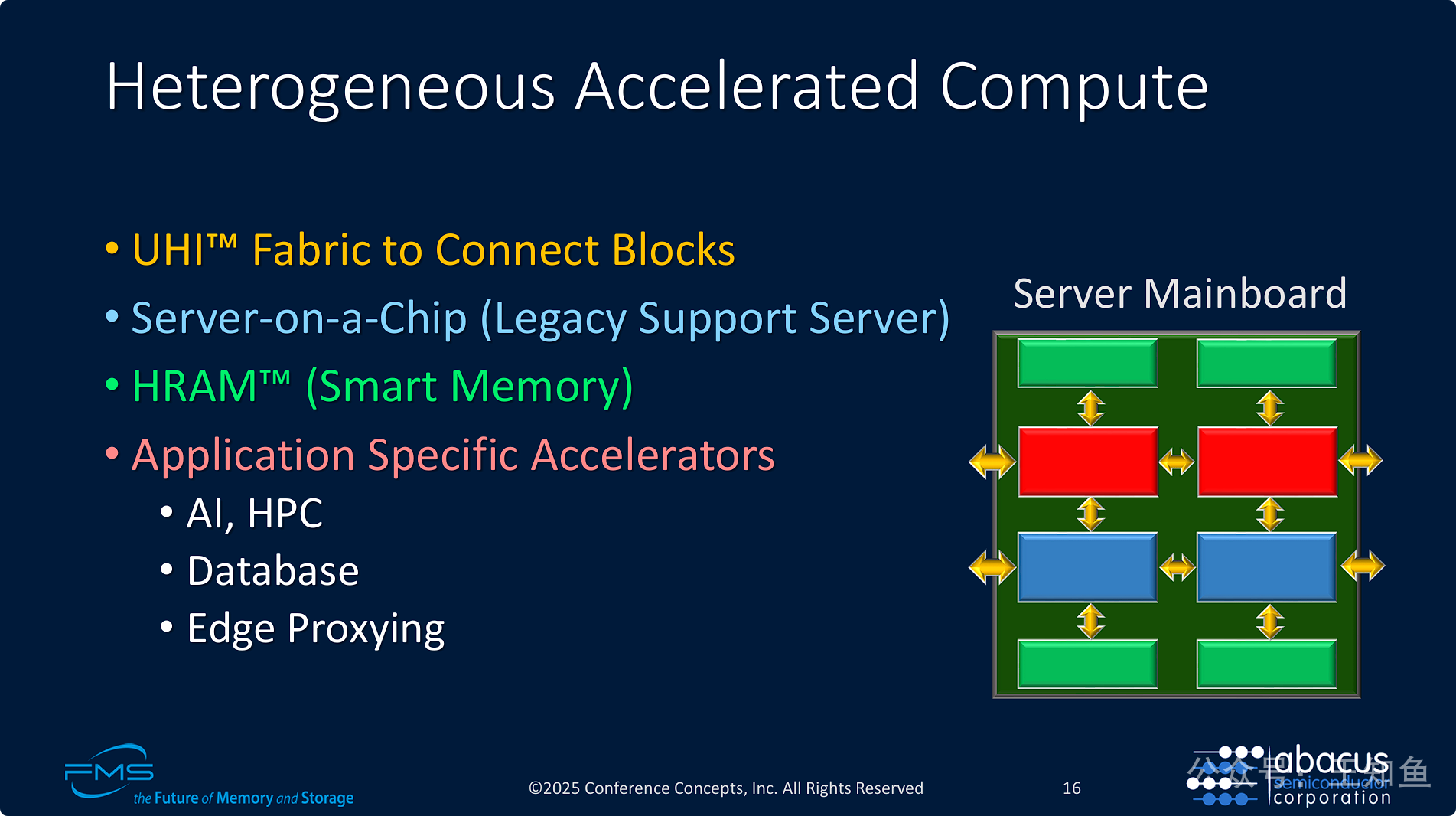

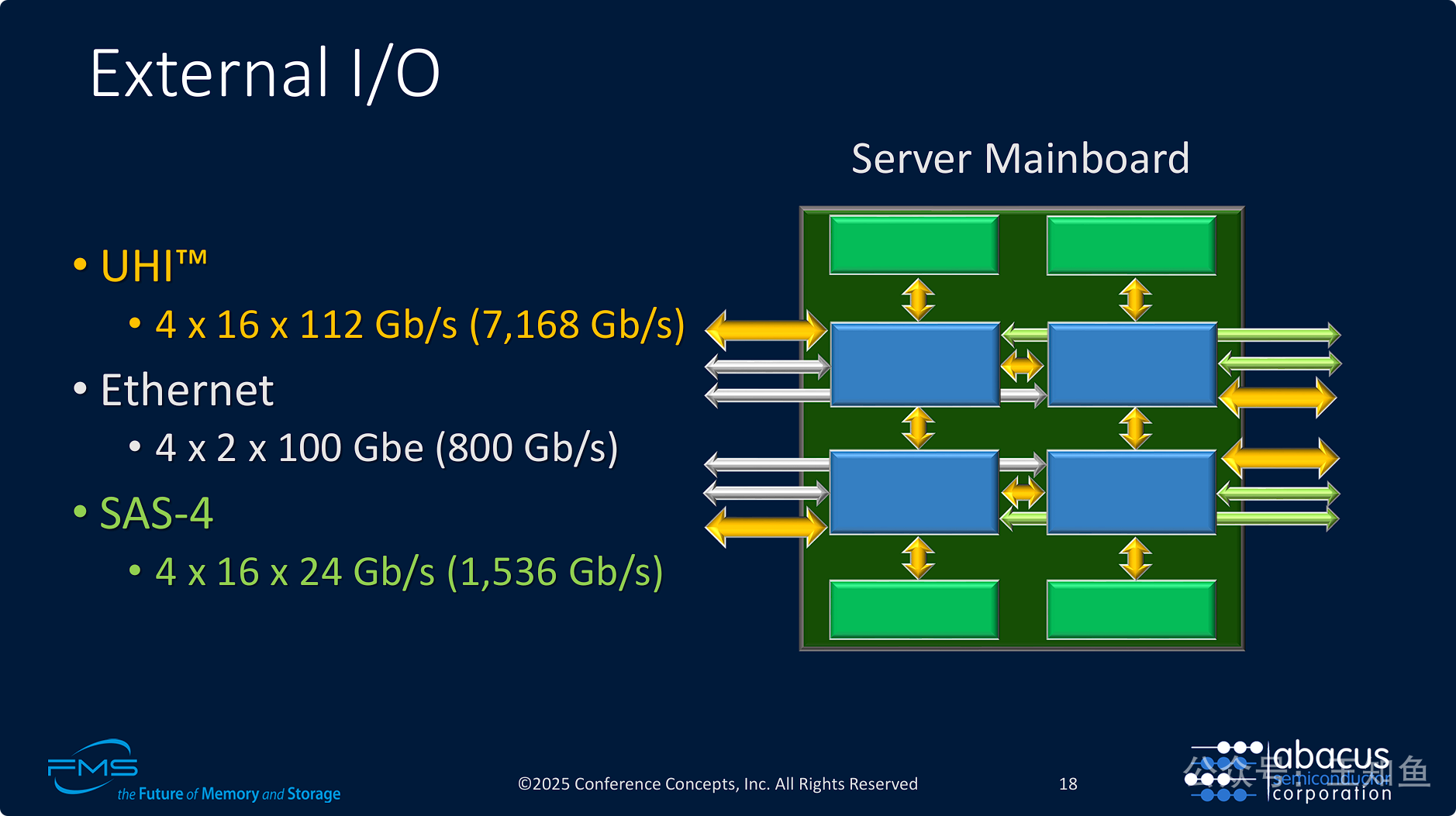

图展示了一个名为“Server Mainboard”(服务器主板)的平台。这个主板上没有传统的CPU插槽和内存插槽,而是像一块“乐高”底板,可以插上不同功能的模块化芯片。

箭头代表 UHI™ Fabric (UHI互连网络),它像神经网络一样将主板上所有的模块连接在一起,形成一个统一的高速数据交换网络。箭头不仅连接了相邻模块,也指向外部,意味着该主板可以与其他主板互连,构建更大的集群。

-

架构核心思想: 其核心是 “解耦/分解”(Disaggregation) 。传统的服务器将计算、内存、I/O紧紧绑定在一起;而Abacus的架构将这些功能分解成独立的模块(SoC、HRAM、加速器),然后通过统一的 UHI™ Fabric 将它们灵活地重新组合起来。

-

平台的灵活性与可扩展性: 用户可以根据自己的需求,像搭积木一样配置服务器。

-

需要一个高性能存储服务器?那就多配置几个

Server-on-a-Chip和HRAM模块。 -

需要一个AI训练平台?那就保留少量的SoC作为主控,然后插入大量的AI加速器和HRAM模块。

-

===

UHI 底层通信协议是基于PCIe的吗?GPU互联需要极高的带宽,因此NVlink成为核心技术,而其他chiplet,如CPU和网络IO等,并不需要同等带宽,UHI是如何权衡不同chiplet之间的差异化需求,做到统一互联的?参考业界的互联方案,是将高性能组件通过UAlink互联,外围通过UEC互联

UHI 底层通信协议是基于PCIe的吗?

大概率是,至少在物理层(PHY)上是兼容或基于PCIe 6.0技术的。

虽然PPT没有明说“UHI就是PCIe”,但有几个强有力的证据:

-

112G SerDes: 这是最关键的技术指标。UHI建立在112Gbps的SerDes物理层之上。这与 PCIe 6.0 规范所采用的电气标准完全相同(112G PAM4信令)。这意味着从最底层的硬件、信号完整性、连接器等角度来看,UHI的物理层与PCIe 6.0是同源的。

-

I/O Chiplet: 在“Server on a Chip”那一页,明确提到I/O Chiplet支持PCIe。这表明Abacus的系统需要与标准的PCIe生态系统进行交互。采用一个兼容的物理层可以极大地简化设计、复用IP并保证兼容性。

在此基础上,再来作者试图比较:UHI、Ethernet和SAS,只觉得场景有点混淆,脱离场景谈性能,大概率是说不明白的,故不展开。

===

报告的材料应该有删减,整理过程思路和问题意识不是很集中。

主旨是介绍UHI 互联通信协议(大概率基于PCIe),大篇幅讨论基于UHI构建 Chiplet 专用芯片,头尾又在介绍HDD场景需求,UHI在HDD领域的应用价值,没有凸显出来 。

基于PCIe 构建CPU-CPU,GPU-GPU 之间的互联,似乎不是业界的重点,但Chiplet高度自定义片上系统的互联,的确是未来数据中心Node节点内竞争的关键。Nvidia 和 Intel 合作已经预示了产业界方向。