DDR5内存纠错革新:RAIDDR如何平衡成本与可靠性

问题意识

Solution for Excessive Memory Overheads : RAIDDR ECC code

Terry Grunzke – Microsoft Azure

背景介绍

在数据中心和服务器领域,内存可靠性直接关系到系统稳定性与数据安全。随着DDR5技术的普及,我们面临一个关键挑战:如何在提升性能的同时控制不断增长的ECC开销?传统方案中,x4架构虽能实现完整的Chipkill保护,但成本高昂;而x8架构成本较低,却牺牲了关键可靠性。

微软Azure团队提出的RAIDDR技术,正试图打破这一僵局。这项创新方案通过将部分纠错计算从内存条转移到主机控制器,实现了硬件精简与可靠性提升的双重目标。RAIDDR不仅支持标准Chipkill功能,还能提供更强的SDDC+1保护级别,为x8内存架构在服务器应用中的可行性开辟了新路径。

面对日益复杂的计算需求,我们是否真的需要在成本与可靠性之间做出妥协?RAIDDR的出现,或许标志着内存纠错技术从纯硬件方案向智能协同设计的重大转变。

读者收获要点

技术架构洞察:深入理解DDR5 x4与x8架构在可靠性设计上的根本差异,掌握Chipkill技术的工作原理及其在服务器环境中的实际价值。

成本效益分析:学会评估不同ECC方案的总拥有成本,包括物料成本、功耗开销和系统可靠性之间的权衡关系。

创新方案应用:了解RAIDDR技术的核心原理,掌握如何通过软硬件协同设计实现超越传统方案的纠错能力。

实践决策指导:获得在实际项目中根据应用场景选择最优内存架构的方法论,平衡性能、可靠性和成本需求。

开放性问题

技术演进方向:随着AI和边缘计算的兴起,传统服务器内存架构是否面临重构?RAIDDR这类软硬件协同方案是否会成为未来内存技术的主流发展方向?

产业生态影响:RAIDDR的开源特性将如何改变内存技术市场的竞争格局?芯片厂商、服务器制造商和云服务提供商需要如何调整各自的战略定位?

可靠性边界探索:在追求极致可靠性的过程中,我们是否已经接近物理极限?下一代内存技术应该在哪些维度上进行突破,才能实现成本与可靠性的最佳平衡?

👉 划线高亮 观点批注

Main

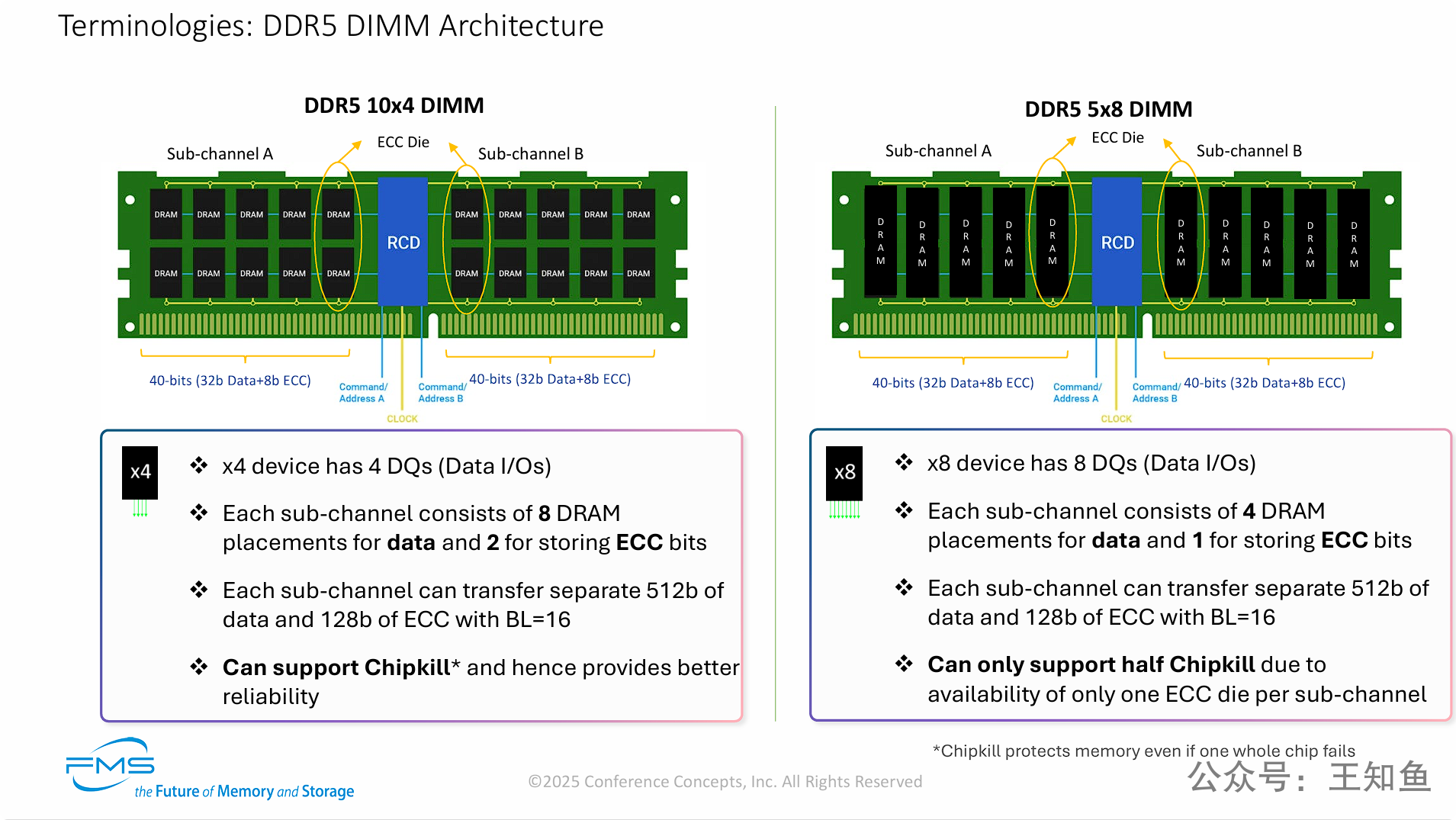

PPT的核心观点是,DDR5 ECC DIMM的可靠性水平(特别是支持Chipkill的能力)直接取决于其所使用的DRAM芯片的位宽(x4或x8)和组织方式。

-

架构对比:PPT通过对比两种常见的DDR5 ECC DIMM(基于x4芯片和基于x8芯片)的物理实现,阐释了它们在芯片数量和布局上的差异,尽管它们都实现了相同的32位数据+8位ECC的子通道逻辑宽度。

-

可靠性的关键差异:

-

x4 DIMM由于将ECC位分散到两颗独立的芯片上,能够实现完整的Chipkill功能,可以容忍任意单个DRAM芯片的完全故障,因此具有更高的系统可靠性。

-

x8 DIMM将所有ECC位集中在单颗芯片上,这成为其可靠性的瓶颈,导致它无法支持完整的Chipkill,只能提供较低级别的保护(称为half Chipkill)。

-

-

设计权衡(Trade-off):这张图揭示了服务器和数据中心在选择内存时的一个重要权衡。选择x4 DIMM意味着需要更多的DRAM芯片(每通道10颗 vs 5颗),可能带来更高的成本和更复杂的布线设计,但换来的是最高级别的内存可靠性。而选择x8 DIMM则可以用更少的芯片实现相同容量,但牺牲了顶级的容错能力。因此,对于关键任务型应用,x4架构是更优选。

什么是Chipkill?

Chipkill 是一种高级的、用于内存的错误检查和纠正(ECC)技术,它的核心目标是保护内存系统能够承受一整颗DRAM芯片(Chip/Die)的完全失效,而不会导致数据丢失或系统崩溃。

您可以把它理解为内存领域的“RAID”技术。

标准ECC (Standard ECC): 传统的ECC内存主要设计用来检测和纠正单个比特(single-bit)的错误。如果在一个数据字中有一个比特位因为电子干扰等原因从0变成了1,标准ECC可以发现并修复它。但如果一整颗DRAM芯片因为物理损坏而出现故障,会导致多个比特同时出错,这超出了标准ECC的处理能力,系统通常会崩溃。

Chipkill技术: 它通过更复杂的算法,将数据和校验信息“条带化(striping)”地分布到内存模组(DIMM)上的多颗DRAM芯片中。当其中任意一颗芯片完全失效时,内存控制器可以像RAID阵列重建故障硬盘的数据一样,利用剩下芯片中的数据和校验信息,通过数学运算实时地重建出故障芯片应该输出的数据。

为什么Chipkill很重要? 随着DRAM工艺越来越先进,芯片密度越来越高,单个比特的“软错误”相对减少,而由制造缺陷、电压不稳或物理老化导致的整颗芯片“硬故障”的风险却在增加。对于要求7x24小时不间断运行的服务器和数据中心来说,因一颗内存芯片故障就导致宕机是不可接受的。Chipkill正是为了应对这种更严重的故障模式而生的。

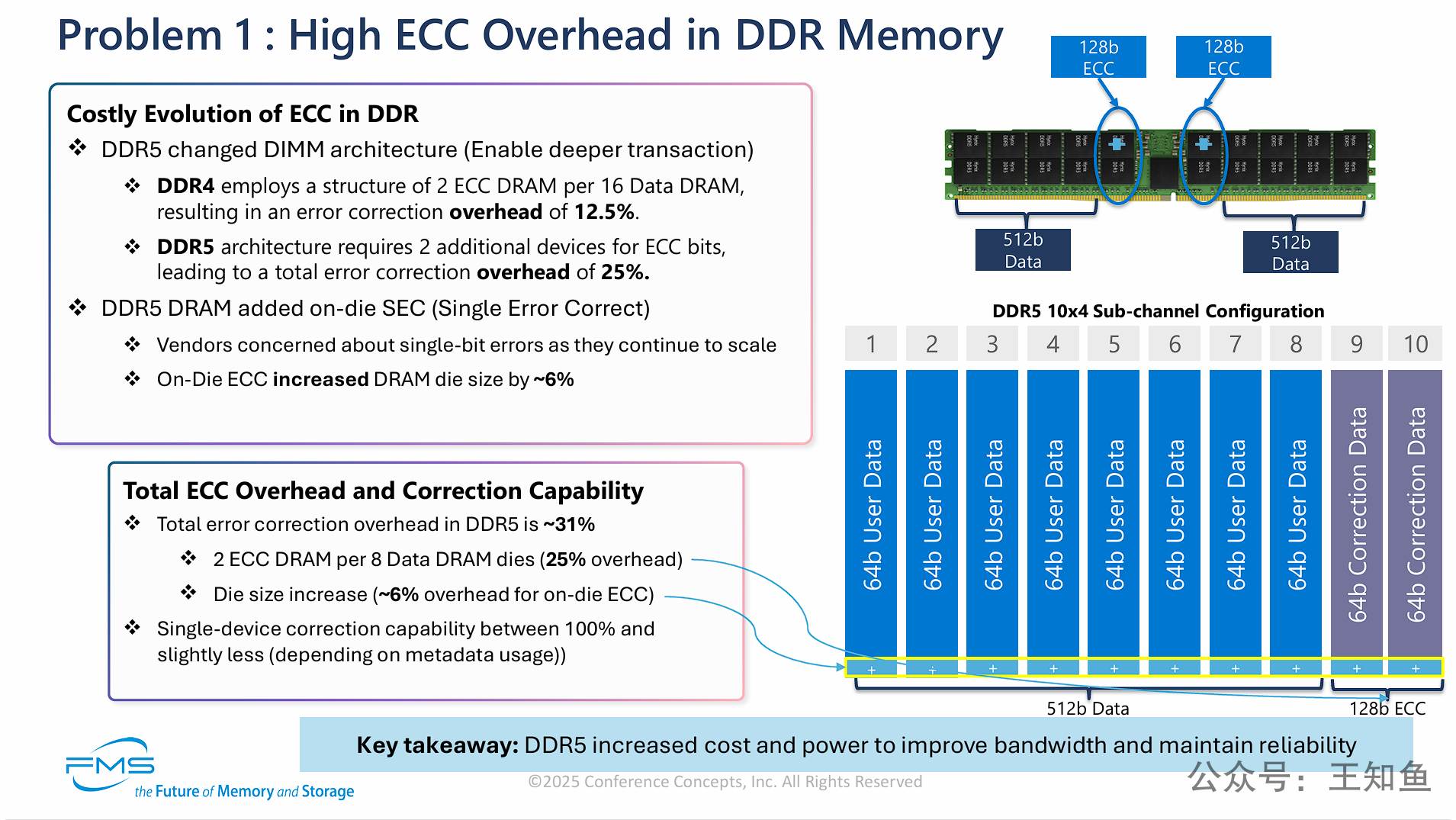

DDR5内存为了在大幅提升带宽和密度的同时保证数据可靠性,付出了显著增加的ECC开销,其总开销高达约31%。

-

DDR5 ECC开销的构成:DDR5(10x4)的总ECC开销由两部分组成:

-

25%的架构开销:由于采用了每8颗数据芯片配备2颗ECC芯片的模式,其外部ECC开销是DDR4(12.5%)的两倍。

-

约6%的芯片级开销:所有DRAM芯片都集成了On-die ECC功能,导致芯片物理尺寸增大约6%。

-

-

开销背后的驱动力:这种高昂的开销并非凭空产生,而是技术发展的必然结果。随着DRAM工艺向更小尺寸演进,数据出错的风险增加,因此必须引入更强的纠错机制(如On-die ECC和更强的外部ECC)来维持系统稳定性。

-

性能与成本的权衡:PPT的最终结论点明了DDR5设计哲学的核心——这是一个典型的工程权衡。用户获得更高带宽和更高可靠性的同时,必须接受因此而来的更高制造成本和潜在的更高功耗。这张幻灯片将DDR5的“高ECC开销”定义为一个需要正视的“问题”,同时也是为实现其技术目标所必须付出的“代价”。

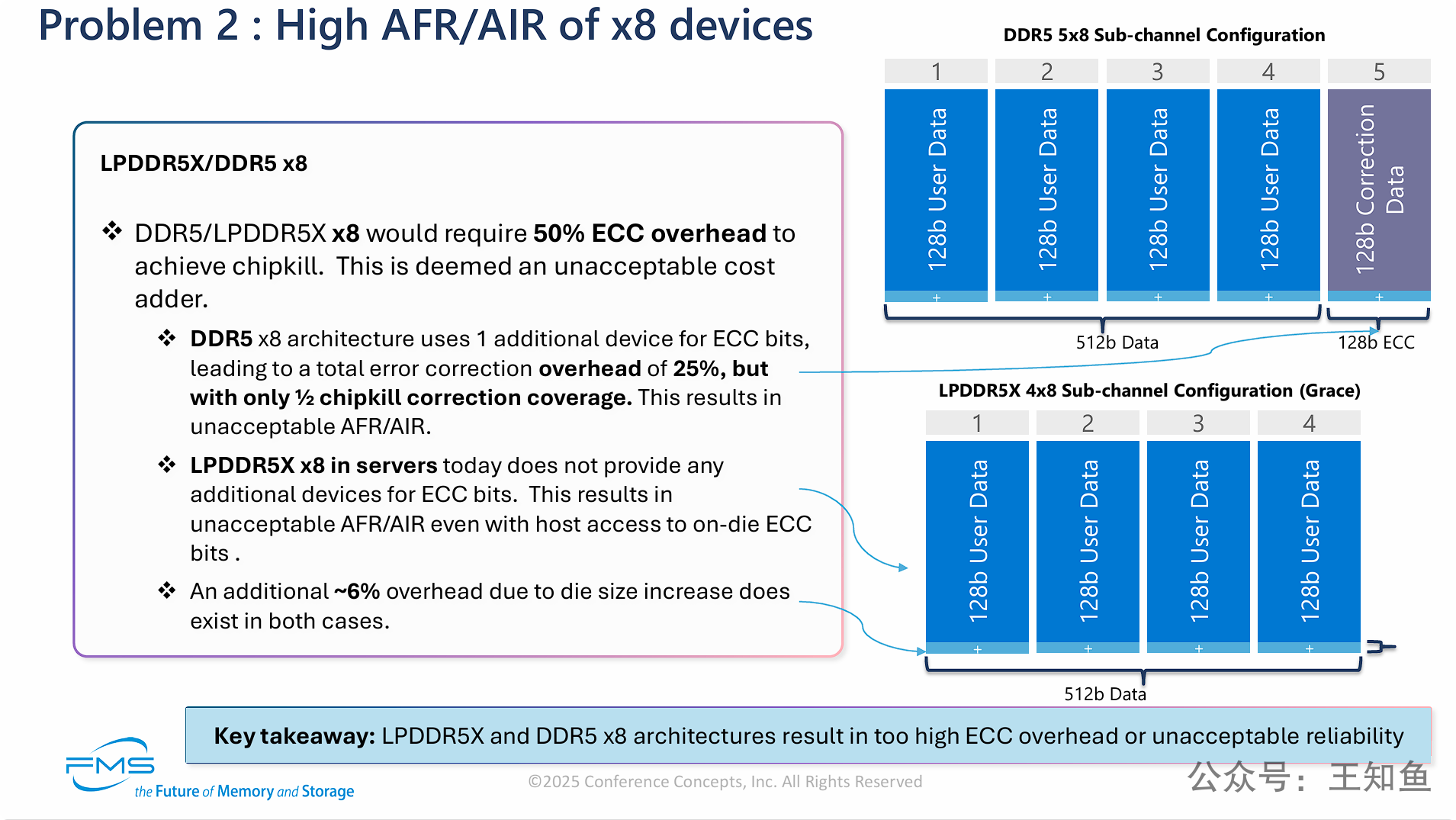

PPT的核心观点是,基于x8位宽DRAM颗粒的内存架构(无论是DDR5还是LPDDR5X)存在一个根本性的两难困境,使其不适合用于对可靠性有严苛要求的服务器等应用场景。

-

两难选择的困境:对于x8内存架构,设计者被迫在两个不良选项中做出选择:

-

追求高可靠性:若要实现完整的Chipkill保护,需要付出高达50%的ECC开销,这在商业上是不可行的。

-

控制成本:若要将ECC开销控制在可接受范围,则会牺牲可靠性,导致系统年化故障率过高。具体表现为:

-

DDR5 x8方案:采用25%的开销,但只能实现“半Chipkill”,可靠性不达标。

-

LPDDR5X x8方案:通常采用0%的外部ECC开销,可靠性更差。

-

-

-

x8架构的内在缺陷:该PPT旨在说明,问题不在于DDR5或LPDDR5X技术本身,而在于采用“x8”这种较宽位宽的颗粒来构建高可靠性内存系统时存在的内在结构性缺陷。

-

对x4架构的侧面印证:通过论证x8架构的种种弊端,这张PPT间接强化了第一张幻灯片中的观点——即x4架构是实现高可靠性服务器内存(支持完整Chipkill且开销合理)的更优选择。

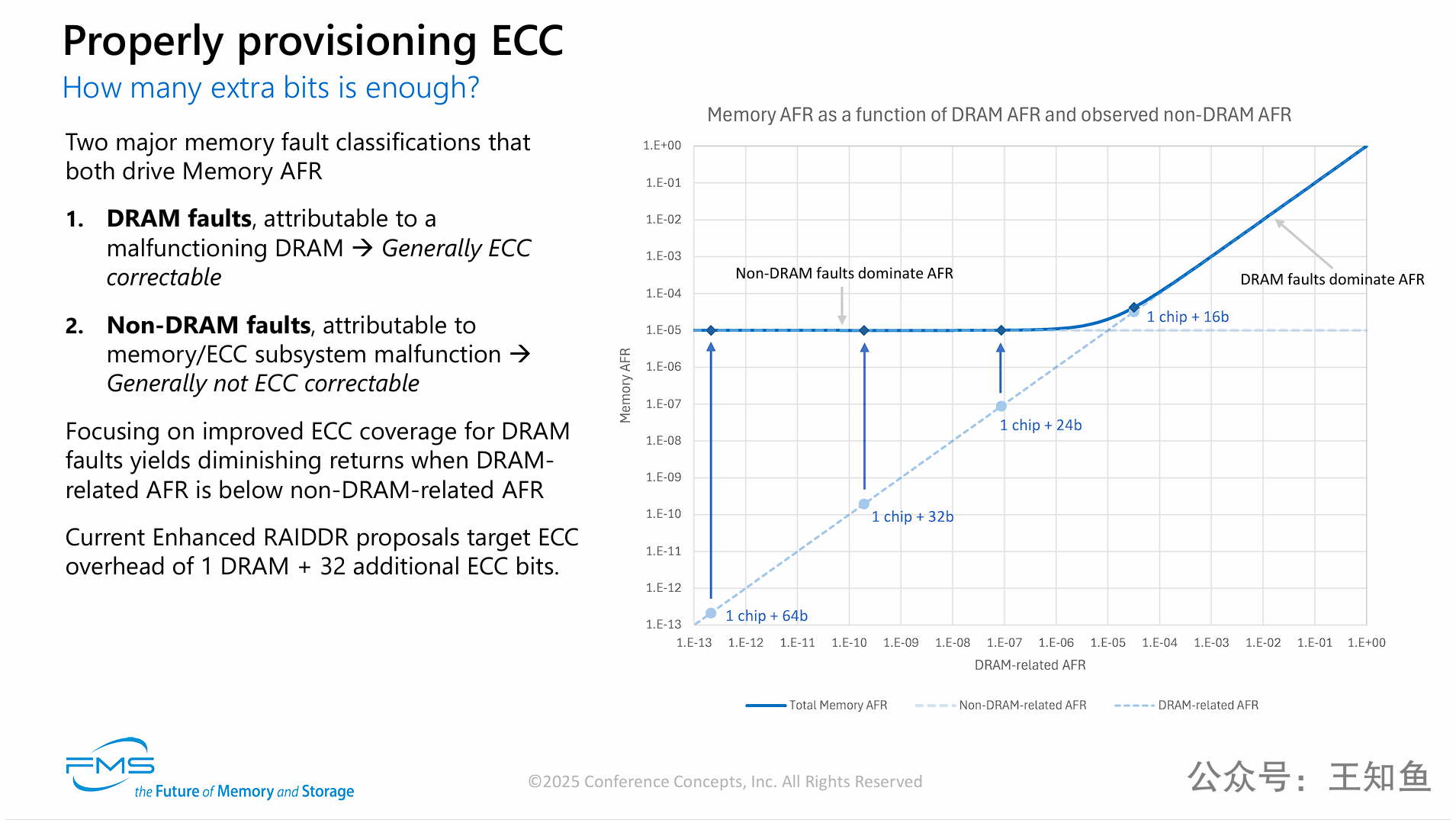

PPT的核心观点是,ECC的配置并非越强越好,而应追求一种平衡,即“合理配置”(Properly provisioning),以避免因过度投资于ECC而产生的“收益递减”效应。

-

系统可靠性的双重瓶颈:一个内存系统的整体可靠性受到两方面因素的制约:可被ECC纠正的DRAM故障和不可被ECC纠正的非DRAM故障。系统的最终可靠性水平取决于这两者中的短板。

-

ECC的“收益递减”效应:一旦ECC的能力足够强大,使得DRAM自身的故障率远低于非DRAM子系统的故障率时,非DRAM子系统就成为新的可靠性瓶颈。此时,继续增强ECC(例如增加更多校验位)对提升整个系统的实际可靠性收效甚微,投入产出比极低。

-

最佳ECC配置策略:最经济有效的ECC配置策略,是使经过ECC校正后的DRAM相关故障率(DRAM-related AFR)与非DRAM相关故障率(Non-DRAM-related AFR)相匹配或略优。过度配置(例如图中

1 chip + 64b的方案)会造成不必要的成本浪费,因为它所解决的问题已不再是系统的主要矛盾。

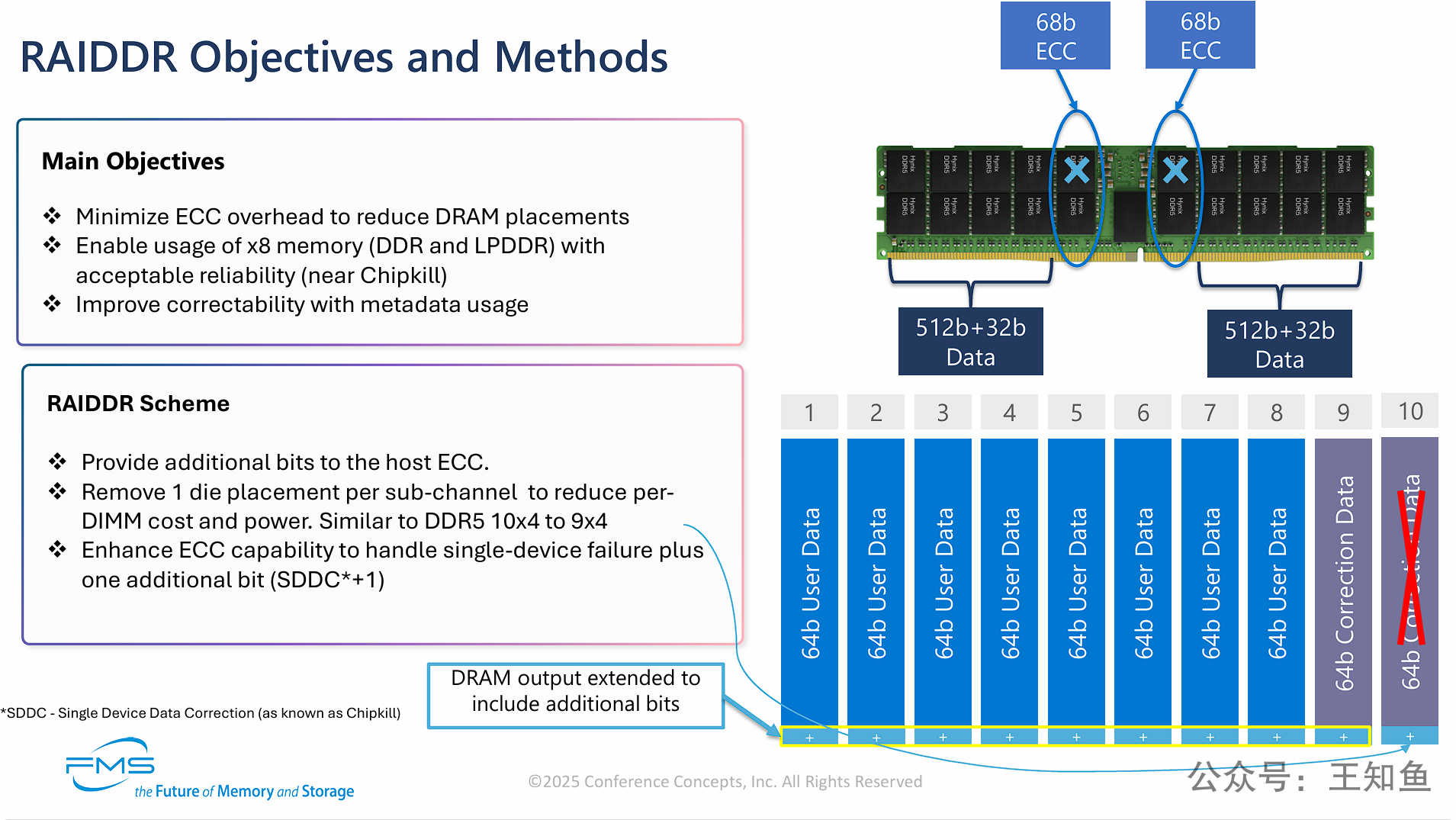

PPT的核心观点是,RAIDDR是一种创新的ECC方案,它通过减少物理芯片数量、扩展DRAM数据输出并利用主机处理能力,旨在以更低的成本实现比传统Chipkill更高的内存可靠性,特别是解决x8内存的应用困境。

-

目标:兼顾成本与可靠性:RAIDDR的首要目标是打破“高可靠性=高成本”的常规,尤其希望让价格更具优势的x8颗粒内存也能安全地用于对可靠性要求极高的服务器等场景。

-

核心方法:减少硬件,增强主机:RAIDDR的实现路径非常巧妙,它是一种软硬结合的思路:

-

硬件上“减法”:通过移除一颗ECC芯片(例如10x4变为9x4),直接降低了DIMM的物料成本和功耗。

-

数据上“加法”:让所有剩余的DRAM芯片在工作时都额外输出少量元数据(metadata)。

-

处理上“转移”:将复杂的、能力更强的ECC计算任务从DIMM转移到算力更强大的主机内存控制器上。

-

-

成果:超越Chipkill的可靠性:最终目标是实现“SDDC+1”的纠错能力,即在能够抵御一整颗DRAM芯片失效的同时,还能纠正一个额外的比特错误,这比标准的Chipkill/SDDC更进了一步。RAIDDR代表了内存纠错技术从纯硬件方案向更智能、更高效的协同设计方案演进的趋势。

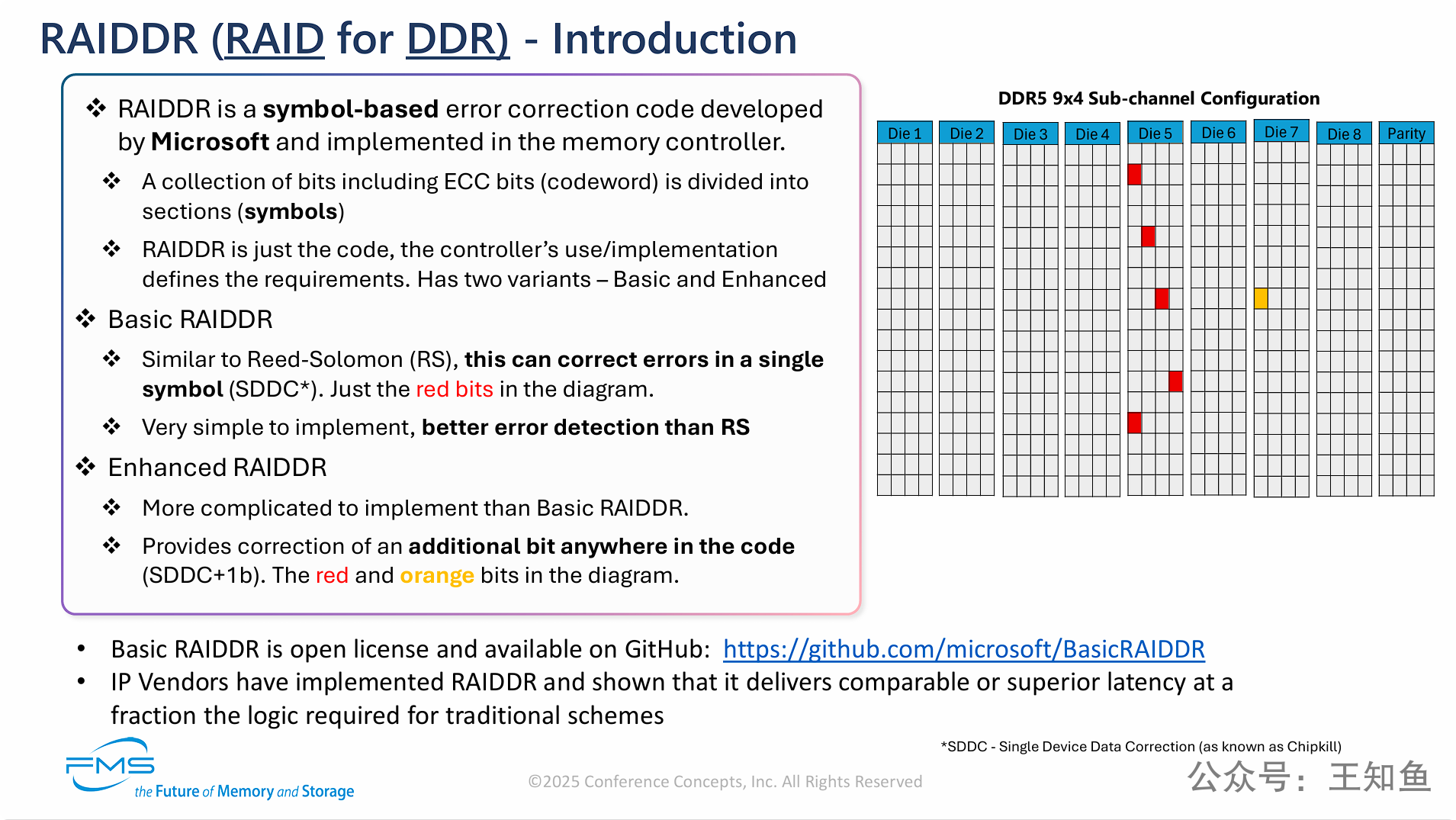

PPT的核心观点是,RAIDDR是微软开发的一种先进、高效、开放的内存纠错技术,它通过在主机内存控制器中实现基于符号的纠错算法,提供了从Chipkill到超越Chipkill(SDDC+1)两个级别的强大保护。

-

技术身份明确: RAIDDR是微软主导开发的、运行在主机侧的、基于符号的ECC方案。其开源特性降低了使用门槛。

-

分级保护能力: 它提供两种不同级别的保护,满足不同需求:

-

基础版:提供业界标准的Chipkill(SDDC)保护,实现简单且高效。

-

增强版:提供“SDDC+1”的超强保护,能应对更复杂的复合型错误场景。

-

-

高效性与实用性: RAIDDR不仅纠错能力强,而且在实际应用中已被证明具有低延迟和低硬件开销的优点,使其成为一个兼具性能、成本和可靠性的理想解决方案。

-

直观的能力证明: 右侧的图表通过一个具体的“整颗芯片失效+单比特错误”的复合场景,无可辩驳地展示了增强版RAIDDR的卓越纠错能力,极具说服力。

===

RAIDDR的内在总逻辑:它是一种将纠错的“智能”从内存条硬件(DIMM)部分转移到主机处理器(CPU/内存控制器)的策略。通过这种转移,它用主机端强大的计算能力,来换取DIMM端更精简、更低成本的硬件设计,从而打破传统ECC方案中“可靠性”与“成本”的强绑定关系。

1. 针对 10x4 封装布局:优化升级,降本增效

内在逻辑

- 现状:10x4(8数据+2ECC)是实现Chipkill的“黄金标准”,可靠但成本高、功耗大。

- RAIDDR的改变:仅用9颗芯片(8数据+1校验),通过共享元数据和主机算力,实现同等甚至更强的SDDC+1保护。

- 本质:RAIDDR是优化者,在保留x4高可靠性的基础上,精简硬件冗余。

经济价值

- BOM成本降低:每条DIMM省2颗芯片,24条服务器可节省48颗,大幅降低物料成本。

- 运营成本下降:芯片减少带来功耗降低,在大规模数据中心显著节省电费与散热开支,优化TCO。

- 可靠性溢价:实现SDDC+1,高于标准Chipkill,降低数据损坏与停机风险,对金融、科研等关键场景极具价值。

2. 针对 5x8 封装布局:赋能重生,开辟市场

内在逻辑

- 现状:5x8(4数据+1ECC)成本低但可靠性弱,仅为“半Chipkill”,难用于企业级。

- RAIDDR的改变:通过主机端强纠错算法,将低可靠硬件提升至SDDC+1水平。

- 本质:RAIDDR是赋能者,将不可用方案变为高可靠、高性价比的可行选择。

经济价值

- 颠覆性成本优势:x8颗粒成本低于x4,RAIDDR使其可用于服务器,在同等可靠性下实现更低总成本。

- 供应链灵活性:可在x4与x8间自由选择,增强议价力与供应安全。

- 释放LPDDR潜力:使低功耗、高密度的LPDDR内存满足企业级可靠性,为AI集群与边缘计算提供高效新路径。